.jpg)

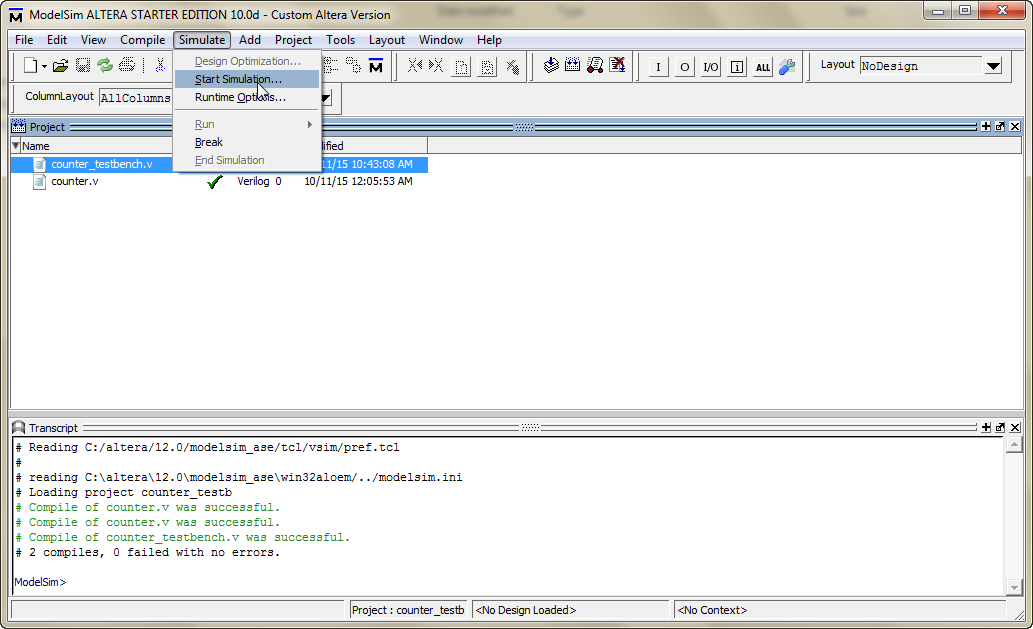

- #Modelsim altera no design loaded for free

- #Modelsim altera no design loaded how to

- #Modelsim altera no design loaded serial

- #Modelsim altera no design loaded software

- #Modelsim altera no design loaded code

#Modelsim altera no design loaded code

We use HDL( Hardware Description Language ) code like Verilog or VHDL to describe a digital circuit, code must be compiled and ultimately implemented into a circuit layout that can be programmed to FPGA device. The code is based on “Non-Restoring Square Root algorithm”. Field Programmable Gate Arrays are a technology that sits between general-purpose microprocessors and fixed-structure Application Specific … Now verify the correctness of your VHDL code, by selecting the "Simulation" button. In previous chapters, some simple designs were introduces e.

After every one of the checks, the code is ready to download into the FPGA USEFUL LINKS to VHDL CODES. 11) Once an LED is lit, it stays on until all eight are on. While the emphasis is on the practical VHDL-to-hardware flow for FPGA devices, this module also provides the essential foundation needed by ASIC designers. The board is the Xilinx Spartan-3 evaluation board which is readily available for ~$200.

#Modelsim altera no design loaded how to

RF and Wireless tutorials VHDL and FPGA Development for Beginners and Intermediates is a course that is designed to teach students how to create and successfully simulate their VHDL design. VHDL affords quicker more accurate designs. If you have a block of … Hi, i need to learn vhdl programming for my final year project. In the case of an SoC FPGA, the hardware-software SoC architecture.

#Modelsim altera no design loaded software

Skills: Verilog / VHDL, FPGA, C Programming, Engineering, Software Architecture Basics of VHDL. VHDL compared with programming languages If you look at VHDL code you will be tempted to think that it is a computer programming language at first glance. ISE WebPACK Design Software is an fully integrated tool for this purpose provided by Xilinx. FPGA programming is the process of configuring or reconfiguring the IC using Hardware Descriptive Languages such as VHDL and Verilog. Programming and Configuring the FPGA Device 7. Download Ebook Fpga Vhdl Sdram Controller Code Hack Create Fpga Vhdl Sdram Controller Code Hack Create When somebody should go to the book stores, search initiation by shop, shelf by shelf, it is in point of fact problematic. It stands for Very High Speed IC Description Language. One of the key features of VHDL is that it is a strongly typed language, which means that each data type (integer, character, or etc. The VHDL compiler is invoked in Line7 to compile the source code for the Addern entity, which is in the parent folder (. This CRC encoder and decoder design have more efficient components. This code will be used for testing the connections and as well the camera output signal. Labels: 1 second delay in vhdl, coding, delay program vhdl, fpga, MIMAS V2 spartan 6 FPGA board, MIMAS V2 spartan 6 FPGA board programming, numato lab, spartan 6, vhdl, vhdl coding, vhdl counter, vhdl fifo, VHDL hardware program, vhdl library, vhdl multiplexer, vhdl mux, vhdl operator, vhdl packages, vhdl reserved words, xilinx Attempts to write VHDL code with a high-level lan-guage style generally result in VHDL code that no one understands.

#Modelsim altera no design loaded serial

This is the base code using by the Mojo V3 to load the FPGA and act as a USB to serial port/ADC for the FPGA.

#Modelsim altera no design loaded for free

Specifically, Xilinx has produced a toolchain called Vitis, which will be available for free from November 1, we're told, and is set to be an alternative to the heavy-duty Vivado suite. This language was first introduced in 1981 for the department of Defense (DoD) under the VHSIC program.

VHDL language is a hardware description language used in electronic design automation to describe digital and From the results presented above, we may conclude that although the automatically generated VHDL code using MATLAB HDL-Coder is straightforward and easier than the manually written VHDL code, but it is not optimized in all comparison parameters shown in Tables 3 and 4 for the chaotic and hyper-chaotic systems. The Fast-Track is for absolute FPGA beginners. Vhdl code for fpga programming Tessier vhdl1 Description: Designs four ways according to the selector, its function is chooses four groups of different data according to the request an output Output that group of data has two controls signals to decide, its truth table as follows: Data access control end output data Input0 Input1 output 0 0 output0 0 1 output1 1 0 output 21 1 output 3 - This structural code instantiate the ODD_PARITY_TB module to create a - testbench for the odd_parity_TB design.

0 kommentar(er)

0 kommentar(er)